Synchronous Filp Flop

An R-S flip-flop output changes the state as soon as inputs change. If the inputs change at irregular intervals, the outputs will also change. For this very reason, the aforementioned circuit is at times called an asynchronous flip-flop.A synchronous flip-flop changes state at certain times only. The change-of-state times are determined by the circuit called as clock. The clock puts out a continuous train of pulses at the regular intervals.

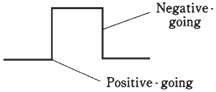

There are different ways in which the synchronous flip flop can be triggered, or made to change the state of it.In static triggering, outputs can change state only when the clock signal is high or low. This kind of circuit is sometimes called as gated flip-flop.In the positive-edge triggering, outputs change state at instant the clock signal goes from low to high, which means, while the clock pulse is positive-going. The term edge triggering derives from the fact that abrupt rise or fall of the pulse looks like the edge of a cliff. In the negative-edge triggering, the outputs change state at instant the clock signal goes from high to low, or when pulse is negative-going.

Figure-Pulse edges are either positive-going or negative-going.