R-S Flip Flop

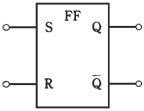

In diagrams, a flip-flop is usually shown as a rectangle with 2 or more inputs and 2 outputs. If the rectangle symbol is used, letters FF, for flip-flop, are printed or written inside at top.The inputs of an R-S flip-flop are labeled as R (reset) and S (set). The outputs are Q and − Q. (Often, instead of − Q, you will see Q , or perhaps Q with the line over it.) As their symbols imply, the 2 outputs are always in logically opposite states. The symbol for the R-S flip-flop is shown in the figure given below.

Figure--Schematic symbol for an R-S flip-flop.

In the R-S flip-flop, if R=0 and S=0, the output states don’t change; they stay at whatever values they are already at. If R=0 and S=1, then Q=1 and − Q=0. If R=1 and S=0, then Q=0 and − Q=1. This means, the Q and − Q outputs will attain these values, no matter what states they were at before.

But if S=1 and R=1, things become bizarre. The flip-flop becomes unpredictable. Due to this, engineers avoid letting logic ls get into both the inputs of the R-S flip flop.

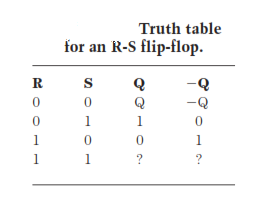

Table given below is the truth table for the R-S flip-flop.