Voltage Amplification:

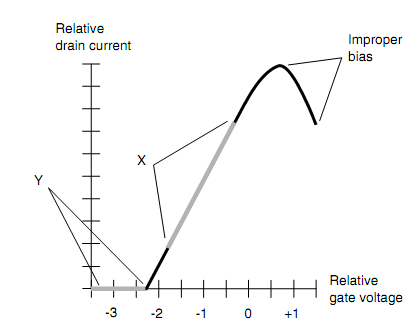

The graph in figure below shows the drain channel current, ID like a function of the gate bias voltage EG for a theoretical n-channel JFET whenever no signal is applied to the gate electrode. The drain voltage ED is supposed to be constant.

Whenever EG is pretty negative and large, the JFET is pinched off, and no current flows via the channel. Since EG acquires less negative, the channel open up, and current begins flowing. As EG acquires still less negative, the channel gets broader, and the current ID rises. Since EG approaches the point where the source-gate (S-G) junction is at forward breakover, the channel conducts and also it possibly can. When EG become positive sufficient, therefore the S-G junction conducts, and the JFET no longer works correctly. Some of the current in the channel is shunted via the gate. This is similar to a garden hose springing a leak.

The best amplification for weak signals is acquired whenever EG is such that the slope of the curve in figure below is steepest. This is shown approximately by the range marked X in the graph. For power amplification, outcomes are frequently best whenever the JFET is biased at or beyond pinch off, in the variety marked Y.

Figure: Associative drain current as a function of gate voltage in a hypothetical n-channel JFET.