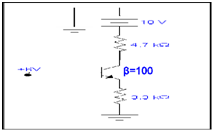

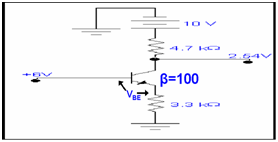

Q Demonstrate the transistor is in saturation.

SOLUTION:

For input loop, using KVL

6 -VBE- IE(3.3k)=0

Rearranging IE= (6-0.7)/3.3k=1.61mA

Thus

IB= IE/101=1.61m/101=15.94mA

Also VE= IERE=1.61m(3.3k)=5.3V

IC=15.94 m(100)=1.59mA

Thus KVL Equation for the output loop is

10-1.59m(4.7k)-VC=0

\ VC=10-7.49=2.50V

QVC<VB,

Thus the transistor is in saturation.