Q. What is Signal Multiplexing?

Frequency-division multiplexing (FDM) and time-division multiplexing (TDM) systems. When data from many sources in time are interlaced, the interlacing of data is called time multiplexing, in which case a single link can handle all sources. Figure (a) illustrates time multiplexing soon after sampling for N similar messages. With proper interleaving of sampling pulses [see Figures (b) and (c) for individual message signal waveforms], the train of samples can be added for the signal at point A in Figure (a), as shown in Figure (d). If we consider N similar messages of spectral extent Wf rad/s, the sampling interval Ts must satisfy

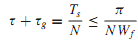

based on the sampling theorem. A time slot is the time per sampling interval that is allowed per message. It is equal to the sum of the sampling-pulse duration τ and separation τg, called the guard time. Thus, we have

The time that is required to gather at least one sample of each message is known as a frame, which is Ts, as shown in Figure (d). Now, with a single composite source of the waveform shown in Figure (d) at point A of Figure (a), the time multiplexer of Figure (a) operates beyond A. For Nb-bit encoding, each time slot in the output PCMsignal will have Nb bits of duration,

It is assumed that all sample trains are derived from the same timing source, called a clock, and hence have the same frequency. Instead of using up all frame time for messages, some time is usually allocated for synchronization so that the receiver will know the start times of frames.