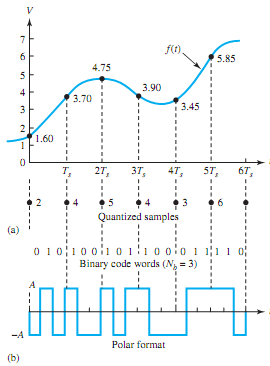

Q. Show Quantization process

Let Figure (a) illustrate a message f (t) with values between 0 and 7 V. A sequence of exact samples taken at uniform intervals of time is shown: 1.60, 3.70, 4.75, 3.90, 3.45, and 5.85 V. Quantization consists of rounding exact sample values to the nearest of a set of discrete amplitudes called quantum levels. Assuming the quantizer to have eight quantum levels (0, 1, 2, . . . , 7 V), a sequence of quantized samples (2, 4, 5, 4, 3, and 6 V) is shown in Figure (a).

Obviously, the scheme is not limited to messages with only nonnegative voltages. The quantizer is said to be uniform when the step size between any two adjacent quantum levels is a constant, denoted by δv volts. Quantizers with nonuniform step size are also designed for improved system performance. An L-level quantizer can have even or odd L. A quantizer is said to be saturated or overloaded when

Figure shows the output quantum levels versus input voltage characteristic (stairstep in shape) of an L-level quantizer, when themessage signal has both positive and negative amplitudes of the same maximum magnitude. Case (a) corresponds to L being an even integer, when the midriser can be observed; and case (b) corresponds to L being an odd integer, when the midtread can be seen.