Instruction Set Architecture (ISA):

The Instruction Set Architecture (ISA) is the part of the processor which is noticeable to the compiler writer or programmer. The ISA serves as the limit amongst hardware and software. We will deeply describe the instruction sets found in several of the microprocessors used today. The ISA of a processor can be explained by using 5 categories:

Operand Storage in the CPU

- Where are the operands reserved other than in memory?

Number of explicit named operands

- How many operands are named in a distinctive instruction?

Operand location

Can be any no. of ALU instruction operand be located in memory? Or ought to be all operands are kept internally in the CPU?

Operations

What type of operations is provided in the ISA.?

Type and size of operands

What is the size and type of per operand and how is it mention?

In all the above the most distinctive factor is the first. The most common types of ISAs are as following:

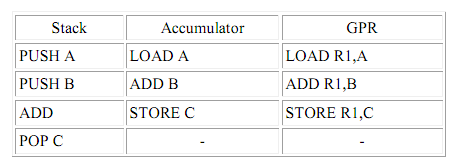

a. Stack: - The operands are put implicitly on top of the stack.

b. Accumulator:-One operand is implicitly mentions in the accumulator.

c. General Purpose Register (GPR) - All operands are explicitly specified, they are either memory locations or registers.

Assembly code of

A = B + C;

in all of the above three architectures:

Notice the fact that every processor may be neatly tagged into any 1 of the above categories. The i8086 contain much instruction that use implicit operands though it has a general register set. The i8051 is another instance, it has four banks of GPRs but most instructions might have the A register as one of its operands.