FET Parameters

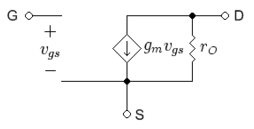

A basic, low-frequency hybrid-pi model for the MOSFET is displayed in figure. The several parameters are as follows.

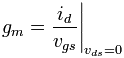

is the transconductance in siemens that evaluated in the Shichman-Hodges model in terms of the Q-point drain current ID by:

Figure: Simplified, low-frequency hybrid-piMOSFET model.

gm = 2ID /VGS = Vth ,

In which:

ID stands for the quiescent drain current (also called the drain bias or DC drain current)

Vth stands for the threshold voltage and

VGS stands for gate-to-source voltage.

The combination:

VoU = (VGS - Vth)

Often is called the overdrive voltage.

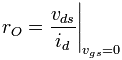

is the output resistance because of channel length modulation, calculated by using the Shichman-Hodges model as

ro = (1/ λ + VDS) / ID ≈ VEL / ID ,

By using the approximation for the channel length modulation parameter λ:

λ = 1/VEL

Where VE is a technology-related parameter (about 4 V/μm for the 65 nm technology node) and L is the length of the source-to-drain separation.

The reciprocal of the output (o/p) resistance is named the drain conductance

gds = 1/ro .