Explain the process of inter-register signalling.

Registers are utilized in common control exchanges to store and analyze routing data.

They are given on a common basis is a single register gives routing data for a number of speech circuits. When a call has been setup, the register is after that made available to set up another calls. And inter register refers to signaling among two registers of dissimilar exchanging.

Signaling systems link the type of transmission systems, subscriber equipments and switching systems in telecommunication network to allow the network to function as an entire. Three types of signaling are included in a telecommunication network as:

1. Subscriber loops signaling.

2. Intra exchange or register signaling

3. Interexchange or inter register signaling

In a telephone network, subscriber loop signaling depends on the kind of a telephone instrument utilized. The inter exchange signaling is internal to the switching system and is heavily dependent on the type and design of a switching system. This varies from one model to other even with similar manufacturer. Such signaling does not include signaling system of the type needed on the switching network. If interexchange signaling takes place in between exchanges along with common control subsystems, this is termed as Inter register signaling. The main reason of Inter register signaling is the exchange of address digits that pass from exchange to exchange upon a link by link basis. Also network wide signaling includes end to end signaling among the originating exchange and the terminating exchange. This form of signaling is termed as line signaling. CCS does not utilize the speech or the data path for signaling. This uses a separate common channel, for passing control signals for information paths or a group of trunks.

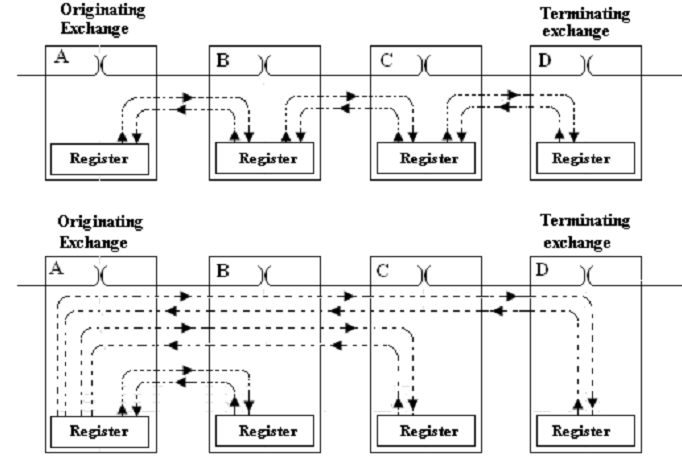

FIG - End-to-end Signaling

For multi link connection in a network of register that controlled exchanges, a register into the originating exchange gets address information by the calling customer and sends out routing digits. All succeeding registers, receives and sends out both routing digits, till the terminating exchange is reached. Such sequence of operation introduces post-dialing delay. An inter-register signaling system cannot be utilized for seize, clear and answer signals. No register is connected while an incoming seize signal is received, because this is the signal that initiate a connection to a register. The register is released after this has set up a connection by its exchange and sent out routing digits; therefore, this cannot get answer and clear signals. Also in-bloc or overlap signaling may be utilized. In en- bloc signaling, the total address information is transferred by one register to the next as signal string of digit. Therefore, no signal is sent out till the complete address information has been got. In overlap signaling, digits are sent out immediately as possible. Therefore, some digits may be sent before the complete address has been acquired and signaling may take place before the complete address has been received and signaling may take place concurrently on two links (that is the signal overlap). The enables next registers to start digit to analyses previous than is possible along with en-bloc signaling and it reduces post-dialing delay. Also link-by- link signaling or end-to-end signaling may be utilized. In the link-by-link signaling, information exchange only among adjacent registers in a multi link connection as demonstrated by figure. In end-to-end signaling, the originating register controls the setting up of a connection till this reaches its last destination, as demonstrated in figure. Each transit register receives simply the address information needed to select the outgoing route to the subsequent exchange in the connection. Containing performed its task, this is released and the originating register signals to the subsequent register.