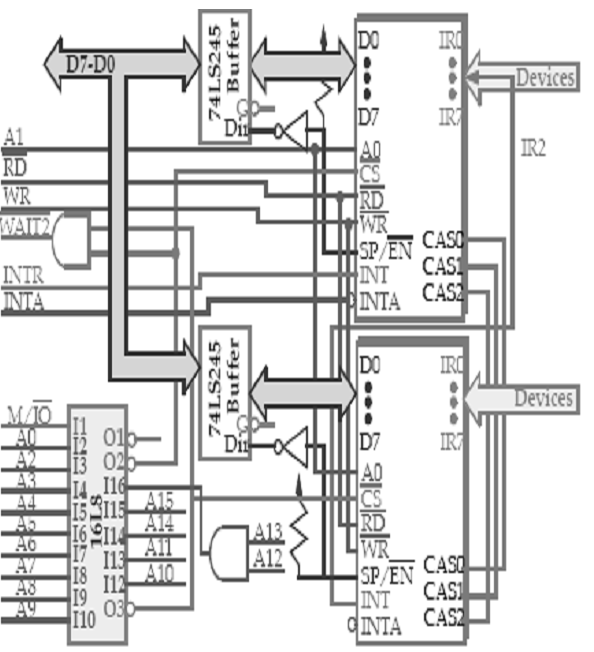

Explain cascading of multiple PICS 8259.

The 8259A adds 8 vectored priority encoded interrupts to the microprocessor. It can be expanded to 64 interrupt requests by using one master 8259A and 8 slave units. CS and WR must be decoded. Other connections are direct to microprocessor. The pins D7 - D0: the bidirectional data connection, IR7 - IR0: Interrupt request, used to request an interrupt & connect to a slave in a system with multiple 8259A.

WR: Attaches to a write strobe signal (lower or upper into a 16 bit system) ,

RD: Attaches to the IORC signal,

INT: Attaches to the INTR pin on the microprocessor from the master and is Attached to a IR pin onto a slave and

INTA: Attaches to the INTA pin onto the microprocessor.

Within a system only the master INTA signal is attached

A0:- Selects various command words with in the 8259A,

CS: Chip select - It enables the 8259A for control and programming,

SP/EN: Slave Program (1 for master, 0 for slave)/Enable Buffer (controls the data bus transceivers in a huge microprocessor based system while in buffered mode) and

CAS2-CAS0: Used as outputs by the master to the slaves into cascaded systems.

Fig: cascading multiple 8259