Balanced Wye-Connected Load

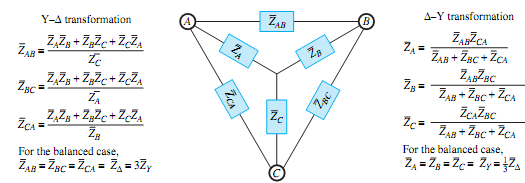

Let us consider a three-phase, four-wire 208-V supply system connected to a balanced wye connected load with an impedance of 10 20° �, as shown in Figure (a). We shall solve for the line currents and draw the corresponding phasor diagram.

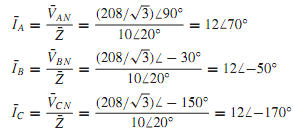

Conventionally it is assumed that 208 V is the rms value of the line-to-line voltage of the supply system, and the phase sequence is positive, or A-B-C, unless mentioned otherwise. The magnitude of the line-to-neutral (or phase) voltages is given by 208/√3, or 120 V. Selecting the line currents returning through the neutral conductor, as shown in Figure, we have

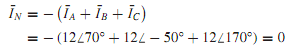

Note that ¯VBC has been chosen arbitrarily as the reference phasor, as in Figure (b). Assuming the direction of the neutral current toward the load as positive, we obtain

That is to say that the system neutral and the star point of the wye-connected load are at the same potential, even if they are not connected together electrically. It makes no difference whether they are interconnected or not.

Thus, for a balanced wye-connected load, the neutral current is always zero. The line currents and phase currents are equal inmagnitude, and the line currents are in phasewith the corresponding phase currents. The line-to-line voltages, in magnitude, are √3 times the phase voltages, and the phase voltages lag the corresponding line voltages by 30°.

The phasor diagram is drawn in Figure(b), from which it can be observed that the balanced line (or phase) currents lag the corresponding line-to-neutral voltages by the impedance

angle (20° in our example). The load power factor is given by cos 20° for our problem, and it is said to be lagging in this case, as the impedance angle is positive and the phase current lags the corresponding phase voltage by that angle.

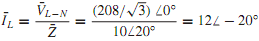

The problem can also be solved in a simpler way by making use of a single-line equivalent circuit, as shown in Figure(c),

in which ¯ VL-N is chosen as the reference for convenience. The magnitude of the line current and the power factor angle are known; the negative sign associated with the angle indicates that the power factor is lagging. By knowing that the line (or phase) currents ¯IA, ¯IB, ¯IC lag their respective voltages ¯VAN, ¯VBN, and ¯VCN by 20°, the phase angles of various voltages and currents, if desired, can be obtained with respect to any chosen reference, such as ¯VBC.