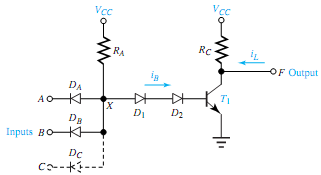

A circuit realization of a NAND gate will now be developed. By connecting NAND gates together in various ways, one can synthesize other gates and flip-flops. Thus in principle, a single NAND gate circuit, repeated many times, would be sufficient to build up digital systems. One possible NAND gate circuit is shown in Figure, in which it can have asmany inputs as desired (indicated by the dashed-line input C), and typical values of VCC = 5V, RA = 2k�, RC = 5k�, and β = 50. We shall now consider the two inputs A and B that are quite adequate for our discussion,with the high range defined to be 4 to 5Vand the lowrange defined to be 0 to 0.5V.

While the input voltages vA and vB are constrained to lie inside the high or low range of the allowed voltage ranges, the resulting output voltage vF is supposed to be inside the high or low range as well. For different combinations of vA and vB, we need to find vF. Since the circuit consists of no less than five nonlinear circuit elements (DA, DB, D1, D2, and T1), an approximation technique is used for analysis, while taking the voltage across a current-carrying forward-biased pn junction to be 0.7 V. The reader may have realized that it is not obvious at the start which diodes are forward-biased and which are reverse-biased. Hence a guessing procedure is used in which a guess is made and checked for self-consistency.

Let us start by letting vA = vB = 0, in which case a probable current path is from VCC down through RA and through inputs A and B. Since this guess implies current flow through DA and DB in the forward direction, wemay guess that the voltage at X is 0.7 V. There is also a current path from X down to ground through D1 and D2 and the base-emitter junction of the transistor. Even though the sign of the guessed voltage is correct to forward-bias these three junctions, its magnitude of 0.7 V is insufficient since 2.1 V (or 3 × 0.7) is needed to make current flow through this path.