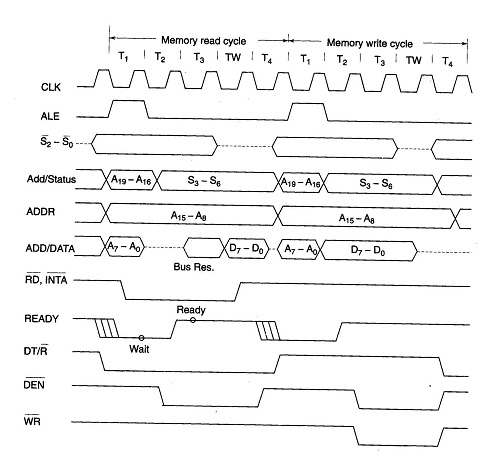

8088 Timing System Diagram

The 8088 address/data bus is divided in 3 parts (a) the lower 8 address/data bits, (b) the middle 8 address bits, and (c) the upper 4 status/address bits. The lower 8 lines are time multiplexed for data bus and address bus. The upper 4 lines are time multiplexed for address bus and status bus. Each of the bus cycles has T1, T2, T3, T4 and Tw states. The ALE signal goes high for one clock cycle in T1. The trailing edge of ALE is used to latch the valid addresses available on the multiplexed lines. They remain valid above the bus for the next cycle (T2). The middle 8 address bits are always present on the bus throughout the bus cycle. The lower order address bus is tristated after T2 to change its direction for read data operation. The real data transfer takes place during T4 and T3. Hence the data lines are valid in T3 / T4. The multiplexed bus is tristated again to be ready for the next bus cycle. The status lines are valid for the multiplexed address/status bus for T2, T3 and T4 clock cycles.

In case of write cycle, the timing diagram is similar to the read cycle except for the validity of data. The data bits are available in the write cycle on the bus for T2, T3, T4, and Tw. At the end of 14, the bus is tristated. The other signals WR, RD, INTA, DT/R, READY and DEN are similar to the 8086 timing diagram. Figure shows the details of read and writes bus cycles of 8088.

With an 8-bit external data bus, the 8088 has been designed for internal 16-bit processing capability. Closely all the internal functions of 8088 are equal to 8086. The 8088 utilized the external bus in the similar way as 8086, but only 8 bits of external data are accessed at a time. While writing or fetching the 16-bit data, the job is performed in 2 consecutive bus cycles. As the software is concerned, the chips are equal except in case of timings. The 8088, thus might take more time for execution of a particular task as compared to 8086.