Reference no: EM13709

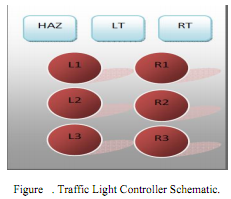

The schematic of the traffic light controller is as shown in figure. There are three control buttons on the panel: HAZ (Hazard), LT (Left) and RT (Right). Whenever, HAZ is clicked, all the six lights blink in unison indicating the situation. However, whenever LT is clicked, only the left three lights (L1, L2 & L3) blink indicating the left turn and similarly, whenever RT is clicked, only the right three lights (R1, R2 & R3) blink indicating the right turn.

Please write the VHDL code fulfilling these specifications. In order to integrate the clicking and display functionality, it is necessary to interface the traffic light code with appropriate mouse and monitor interfacing codes. There are atleast the following number of modules in the correct working of this system:

1) Traffic light controller module.

2) Mouse interfacing module.

3) Monitor interfacing module.

4) Video PLL (a specific code for viewing on the monitor screen).

5) Main module interconnecting the sub-modules through port-mapping.

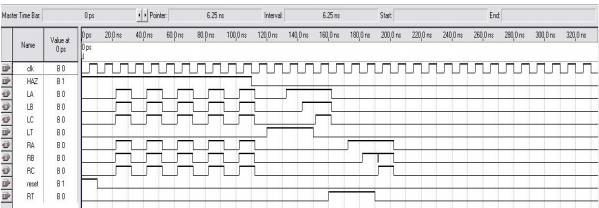

The output:

Lab reports MUST follow the below template:

1) Front page with the title of the project, date and name of the students along with their IDs.

2) Introduction on the working of the system along with a targeted issue that is addressed.

3) Design methodology explaining the hierarchy of the system along with the different modules, their role and respective ports.

4) Results with a detailed explanation of the behavior of the system.

5) Conclusion

6) Problems faced (if any during the coding and implementation phases).

7) Screenshots for simulated waveforms, pin assignments, RTL view and state machine view. (RTL and state machine viewers can be found under Tools -> Netlist Viewers)

8) Contributions containing the names of the individual team members and the name of the modules coded by them.

It should be a hierarchical code having two modules: traffic light module and clock division module. Furthermore, you need to port map

these two modules in a main program.