Reference no: EM13712

PULSE WIDTH MODULATOR

Part-1

Introduction:

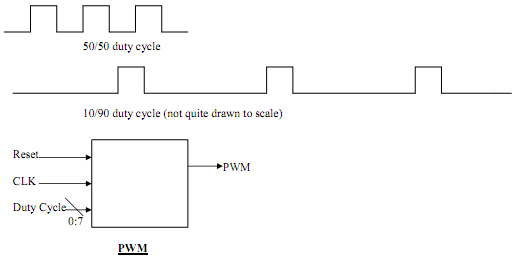

A pulse width modulation (PWM) circuit works by varying the duty cycle of the square wave while keeping the period fixed. In simple terms, it is a technique to provide a logic "1", and a logic "0" for a controlled period of time.

DUTY CYCLE : The duty cycle is the percentage of the period of a square wave that that signal is high. A 50% duty cycle would be high for 50% of the time and low for 50% of the time. Likewise, a 10% duty cycle would be high for 10% and low for 90%.

A block diagram for the system is shown above.

Implementation:

A simple VHDL description of the circuit might look like this:

CONSTANT duty_cycle : INTEGER := A; -- for easy change of duty cycle

Signal count_value : Integer Range 0 to max_value;

Signal PWM : STD_LOGIC;

PROCESS(CLK)

BEGIN

IF RISING_EDGE(CLK) THEN

IF (count_value < max_value) THEN

count_value <= count_value + 1; -- note that we use a counter to keep track

IF (count_value = A) THEN -- of the fraction of the cycle for which PWM is High

PWM <= NOT(PWM); -- toggle PWM Bit

END IF;

ELSE

count_value <= 0;

PWM <= '1'; -- assuming you want to

start with '1' level

END IF;

END IF;

END PROCESS;

This is just one way of implementing the Pulse Width Modulator.

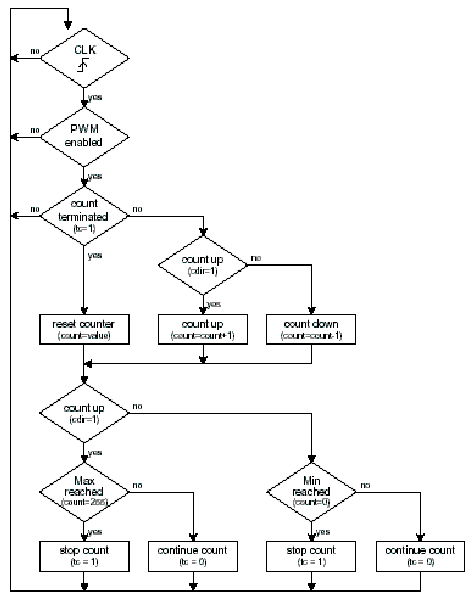

However, for your lab assignment, implement your circuit according to the flow chart given below.

Write and test the VHDL code that represents a description of this PWM circuit using Quartus II.

Hand in your code and a fully documented simulation, being sure to completely describe your design and test methodology.

Part 2:

Use the clock division code that you designed for the traffic light controller in the first lab and for programming the Altera DE-II board. You should be able to demonstrate the change in the turn on times for the LEDs. Use the toggle switches for changing the duty cycle and LEDs as the respective outputs. Prepare an excel sheet for the relevant error compared to the required duty cycle.