Reference no: EM131644

Description:

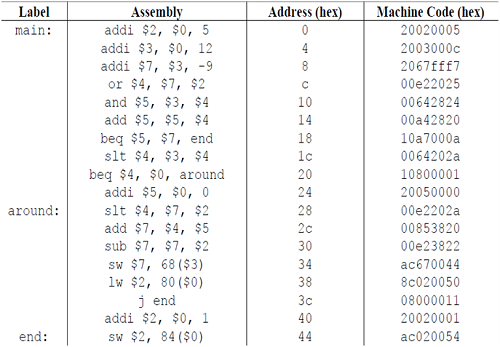

In the process of processor development, functional verification is a crucial step that must be conducted before physical implementation. The purpose of processor functional verification is to find out, via simulation, that if the designed processor (in the form of HDL source code) can execute its supported instructions as the ISA specified. To perform processor functional verification, you will need to write a suite of test cases using the instructions supported by the processor. Each test case has its purpose and its binary format (machine code) will be stored in the processor's instruction memory. The processor to be tested (again, in the form of HDL source code) will then execute the test case code under the control of a software testbench, which is responsible to start/stop the test, and report pass/failure of the test. As an example, a sample MIPS processor test case is shown in Table

Task:

Write a suite of test cases to verify the execution of the following MIPS instructions:

ADD, SUB, AND, OR, SLT, LW, SW, BEQ, J, ADDI, MULT, MFHI, MFLO, JR, JAL, LUI, NOR, XOR, SLL, SLLV, SRA, SRAV, SRL, SRLV, and DIV.

Note that this is an open-ended project. :

1) Showing good verification strategy,

2) Covering more instructions specified by the MIPS ISA.

Requirements:

Purpose:

Composite, ad hoc testing - addi, add, sub, and, or, slt, beq, j, lw, sw

Pass Condition:

The MIPS processor writes the value 7 into address 84 of the data memory.