Reference no: EM13864296

Programming Project on Simulator for APEX

Both project parts require you to submit a hardcopy design documentation, a CD of your code and example results. Both parts also require you to demonstrate your simulator to one of the TAs. Instructions for scheduling the demos will be provided later.

PART 1. Demo to be scheduled with one of the TAs for the period 11/16 to 11/20.

This part of the project requires you to implement a cycle-by-cycle simulator for the simple 5-stage APEX pipeline. Assume that the code to be simulated is stored in a text file with one ascii string representing an instruction (in the symbolic form, such as ADD R1, R4, R6) in each line of the file. The instructions supported are:

• Register-to-register instructions: ADD, SUB, MOVC, MUL, AND, OR, EX-OR (all done on the ALU in a single cycle). You can assume that the result of multiplying two registers will fi into a single register.

• Memory instructions: LOAD, STORE

• Control flow instructions: BZ, BNZ, JUMP, BAL, HALT

Assume that there are 8 architectural registers, R0 through R7. Memory is viewed as a linear array of integer values (4 Bytes wide) numbered 0 through 9999.

The BAL register implements function calls, saves the return address in a special register X and transfers control to a specified target address:

BAL <register>, literal: saves address of next instruction in X and then sets fetch PC to contents of <reg> plus the literal.

The HALT instruction stops execution. JUMP specifies a register and a literal and transfers control to the address obtained by adding the contents of the register to the literal.

To invoke the simulator, you specify the name of the executable and the name of the ascii file that contains the code to be simulated.

Your simulator should have a command interface that allows users to execute the following commands:

Initialize: Initializes the simulator state, sets the PC of the fetch stage to point to the first instruction in the ascii code file, which is assumed to be at address 20000. Each instruction takes 4 bytes of space, so the next instruction is at address 20001, as memory words are 4 Bytes long, just like the integer data items.

Simulate <n>: simulates the number of cycles specified as <n> and waits. Simulation can stop earlier if a HALT instruction is encountered and when the HALT instruction is in the WB stage.

Display: Displays the contents of each stage in the pipeline and the contents of the first 100 memory locations containing data, starting with address 0.

PART 2. Demo to be scheduled with one of the TAs during the finals week.

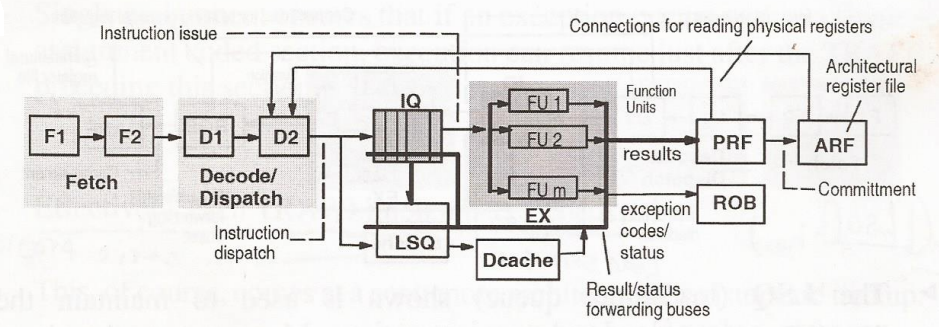

This part requires you to extend and modify your simulator of Part 1 as follows to simulate a datapath that looks like Variation 2. Three function units are present:

• INT (implements integer and logical instructions) - one stage, single cycle latency.

• MUL (implements the MUL operation, non-pipelined, latency 4 cycles,).

• Memory (implements LOAD and STORE instruction, 3 pipeline stages with a single cycle latency per stage.)

The issue queue has 8 entries, the LSQ has 4 entries and the ROB has 16 entries. The physical register file has 16 registers. You can assume that a tag based forwarding mechanism is used.

The command interface is similar to that in Part 1, but the Display command displays, in addition to what is displayed in Part 1, the contents of the architectural and physical registers, what is inside each FU, the rename table, the IQ and ROB, the free list of registers and all structures relevant to renaming, including the tag and result value broadcasted etc. An additional requirement for Part 2 is that you document in detail what each team member did.

• Variation 2: A separate physical register file (PRF) and an architectural register file is used. The ROB entry of an instruction that has a destination register points to the physical register is assigned to hold the result. In this case, the physical registers are called rename buffers. The IBM Power PC 604 implements this design.