Reference no: EM131311158

Setting up a Xilinx project for the BCD Clock

Objective: This document is intended to be used as a reference guide to aid in setting up and working with a Xilinx ISE WebPACK project for use with the BCD clock project.

Project Initiation

1. Create a new Xilinx project as outlined in the "Introduction to Xilinx ISE.pdf" document.

2. Be sure that the XST (VHDL/Verilog) synthesis tool and the ISE simulator are selected as the default simulator for simulation purposes.

3. The project should be initiated with a top-level schematic

Design Entry

1. Regardless of the design entry method used for a particular system subsection (schematic capture or HDL) each subsystem will be integrated within a top-level schematic.

2. For Schematic Capture designs:

a. Design the individual subsystem schematic right on the top-level schematic page and then to cut and paste the design into an associated symbols schematic page or

b. Design the individual subsystem schematic in its already created symbol schematic page.

Symbol Creation

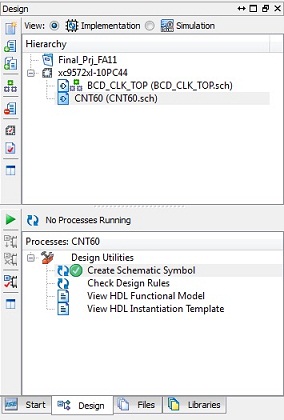

1. Select the schematic that the symbol is desired for from the "Hierarchy" window and then select the "Create Schematic Symbol" option from the "Design Utilities" window as shown in Figure 1.

a. Default symbol is created automatically once the "Process "Create Schematic Symbol" completed successfully" message is written to the "Console" window.

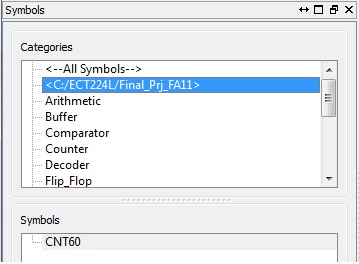

2. The newly created symbol can be selected for addition to any schematic by selecting the symbol from under the current project directory category as shown in Figure 2.

a. The newly added symbol can be edited by right-clicking on the symbol and selecting the "Edit Symbol" option under the "Symbol" category

i. The size and style of the symbol can be changed along with the pin layout

ii. It is recommended that the symbol inputs remain on the left, top, or bottom sides with the symbol outputs on the right side.

Figure 1: Creating a symbol for a selected schematic in Xilinx WebPACK

Figure 2: Selecting a created symbol for addition to a schematic

Subsystem Simulation

Most subsystems of the BCD clock need to be simulated to verify correct operation. When multiple design sources exist for a project, the simulation file must be associated with a single one or with the top-level schematic. There can therefore be multiple simulation files associated with a single project, each testing various subsystem designs. Refer to the document entitled "Digital Circuit Timing Analysis Using Xilinx ISE.pdf" for details on how to setup a simulation using the Xilinx ISE Simulator.

|

Potential entrants residual demand curve

: Suppose the inverse demand is given P=75-0.5Q if the incumbent continues to produce 20 units output, which of the following equations best summarizes the potential entrants residual demand curve?

|

|

How many secret keys are needed to allow secret messages

: In a club with 50 members, how many secret keys are needed to allow secret messages to be exchanged between any pair of members?

|

|

Decrypt the message to get the original plaintext

: Encrypt the message "this is an exercise" using additive cipher with key = 20. Ignore the space between words. Decrypt the message to get the original plaintext.

|

|

Find the type of cipher and key

: Suppose that the alphabet is divided into halves and the letters in the first half are encrypted as the letters in the second and vice versa. Find the type of cipher and key. Encipher the plaintext "an exercise" using the Atbash cipher.

|

|

Design the individual subsystem schematic right on the top

: Design the individual subsystem schematic right on the top-level schematic page and then to cut and paste the design into an associated symbols schematic page or

|

|

Identify and interpret the role of ethics

: ACCOUNTING AND INFORMATION SYSTEMS ACC1AIS - Identify and apply relevant accounting and information systems skills to the development, operation, maintenance and control of accounting information systems and apply the key concepts and principles un..

|

|

Lead to the most recent financial crisis

: Explain the events that lead to the most recent financial crisis. In your opinion, who is to blame?

|

|

Watch the movie and give your reviews

: Analyze for what you consider to be the underlying ideological meaning Of the text. You may want to do background research on your text (understanding both institutional considerations and audience/critical reception) to aid your analysis.

|

|

Decrypt the message by using keys beginning with 1

: Try to decrypt the message by using keys beginning with 1 and continuing until a plaintext appears that makes sense.

|