Pipelining in DSP Processor

Pipelining allows parallel execution of any operations which logically can be performed in parallel. These operations are not required to be the 5 lines listed above, so now let us generalize the 5 lines and name them A, B, C, D and E. Each 1 takes 1 clock cycle and together they make up 1 pass through the loop which is described above. In the given clock cycle pipeline contains 5 different passes each 1 being in just 1 of the 5 states A through E. Therefore any 1 pass would consist of these

5 operations and take 5 clock cycles to complete it. The number of overlapable operations of which 1 pass is comprised is called as depth of pipeline. Here we have depth-5 pipeline.

Characteristic depths are 4 or 5. Some DSP processors have pipeline depths as 11.

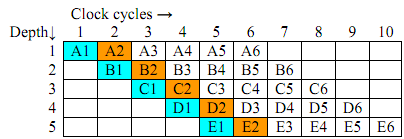

The operation of depth-5 pipeline is shown as follows. Time (clock cycles) runs from the left to right. The height corresponds to distinct hardware stages. There are a total of six product terms being added to accumulator, each term taking five clock cycles. As in {A1 through E1} the 1st product term is added to accumulator and is completed in the clock cycle #5. The addition of 2nd product term, {A2 through E2}, is completed in the clock cycle #6, etc. The complete sum is available in around ten cycles. Without pipeline the summation would take 6 * 5 = 30 cycles.

There is pipeline overhead: at the left there are 4 clock cycles during which the pipeline is filling while at the right there are a further 4 cycles while the pipeline is emptying. (In this specific example the pipeline is full for 2 cycles). For large enough loops the overhead is negligible; therefore the pipeline allows DSP processor to perform 1 multiply-and-add per clock cycle on the average. Generally asymptotically, the processor takes a single clock cycle per instruction only.

In this treatment we are dividing 1 pass through the loop into 2 overlapable parts labeled A through E. In the other contexts an instruction cycle can be divided into perhaps 5 overlapable parts. In above diagram time runs from the left to right, while the depth corresponds to certain hardware units (in this case 5). 1 pass through the loop goes diagonally down from the left to right, shown below in color.

Email based Pipelining assignment help - Pipelining homework help at Expertsmind

Are you finding answers for Pipelining based questions? Ask Pipelining questions and get answers from qualified and experienced Digital signal processing tutors anytime from anywhere 24x7. We at www.expertsmind.com offer Pipelining assignment help -Pipelining homework help and Digital signal processing problem's solution with step by step procedure.

Why Expertsmind for Digital signal processing assignment help service

1. higher degree holder and experienced tutors

2. Punctuality and responsibility of work

3. Quality solution with 100% plagiarism free answers

4. On Time Delivery

5. Privacy of information and details

6. Excellence in solving Digital signal processing queries in excels and word format.

7. Best tutoring assistance 24x7 hours